Shipping records indicate that Intel’s Nova Lake chips are currently undergoing validation (via x86deadandback at NBD). Nova Lake is the successor to Intel’s Arrow Lake series of processors and is expected to debut in 2026-27. While the manifests don’t reveal any key details, it is essential to understand that final specifications are still subject to change.

Going by whispers in the wind, Nova Lake is rumored to employ Coyote Cove P-cores (renamed from Panther Cove) alongside Arctic Wolf E-cores. It is unclear where these architectures currently stand in Intel’s product stack, so we cannot comment on any performance metrics. Ex-CEO Pat Gelsinger confirmed that most of Nova Lake will be produced in-house, likely on Intel 18A, with only a handful of SKUs expected to be outsourced.

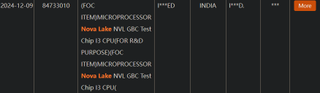

The shipping manifest includes a single entry dating back to December 9th last year, reportedly marked as “FOC,” which should stand for Free Of Charge. The listing explicitly tags the item as a “Microprocessor” and a “Test Chip” labeled “NVL,” shorthand for Nova Lake. Last month, Wildcat Lake reball jigs surfaced similarly at NBD.

Arrow Lake suffers from poor L3 access latency due to an off-die memory controller and a slow ring bus which cripples performance in memory-sensitive applications. A leak alleges that Panther Lake will reintegrate the IMC (Integrated Memory Controller) back into the CPU Tile, similar to Lunar Lake. Likewise, Nova Lake is said to separate the two once again but with added optimizations.

Nova Lake is expected to require a new socket, and unless Intel ports Panther Lake to a desktop, LGA 1851 could be one of the shortest-lived platforms in Intel’s history. In addition, Linux patches indicate Intel is actively developing software support for upcoming CPU generations, including Nova Lake and its supposed successor, “Razor Lake.”

Next-gen E-core-only Clearwater Forest chips will feature Intel’s “Local Cache” technology, designed to compete with AMD’s V-Cache. CPU chiplets, expected to feature the cores and private caches, are placed on top of a Base tile. This Base tile can be configured with varying amounts of shared L3 cache. Sadly, this technology will remain exclusive to Intel’s server counterparts for now but could someday make its way to consumer offerings.

#Intel #ships #Nova #Lake #CPUs #partners #testing #samples #intended #validation #research